# General Relations Between IP2, IP3, and Offsets in Differential Circuits and the Effects of Feedback

A. A. Abidi, *Fellow, IEEE*

**Abstract**—In the presence of offsets, all balanced circuits show an apparent second-order distortion. Differential feedback lowers third-order nonlinearity and also these second-order effects. The results are important for the baseband circuits of zero-IF wireless receivers, which often need a very large second-order intercept point. It is shown that a published analysis of distortion in a bipolar double-balanced mixer is a special case of these general relationships.

## I. INTRODUCTION

INCREASINGLY, the importance of second-order distortion is being recognized as a limitation in the baseband circuits of wireless receivers that downconvert the channel of interest to zero IF. Detection of interferers lying anywhere in the passband by second-order nonlinearity creates spectral components at or close to dc, possibly overwhelming the channel of interest that has been downconverted to zero IF. The main way to combat this effect is with balanced circuits in the baseband. Ideally, when a balanced circuit is stimulated and sensed differentially, it displays no second-order distortion. However, offsets and mismatches in a practical circuit cause small imbalances, which lead to a proportional second-order nonlinearity.

Coffing and Main [1] have analyzed this very effect in a bipolar double-balanced mixer. The exponential  $I$ - $V$  characteristic of the bipolar junction transistor simplifies their analysis and leads to compact expressions for the second-order intercept point (IP2). The question is: How does this analysis extend to other baseband circuits such as fixed- and variable-gain amplifiers and active filters? How is it different for MOS circuits? The purpose of this paper is to show that all of Coffing and Main's results for the input transconductor portion of the bipolar mixer<sup>1</sup> are, in fact, specific instances of properties of any balanced circuit that suffers from an offset.

## II. BALANCED CIRCUITS SUBJECT TO OFFSETS

### IP2

The input–output characteristic of a balanced circuit with differential input and output consists only of odd-order terms [2]

$$v_{\text{out}} = a_1 v_{\text{in}} + a_3 v_{\text{in}}^3 + \dots \quad (1)$$

Manuscript received October 1, 2002.

The author is with the Electrical Engineering Department, University of California at Los Angeles, Los Angeles, CA 90095-1594 USA (e-mail: abidi@icsl.ucla.edu).

Digital Object Identifier 10.1109/TMTT.2003.810147

<sup>1</sup>The analysis of the unequal mark–space ratio in the commuting transistors is not considered here because we are interested in the time-invariant baseband circuits that determine the IP2 of a zero-IF receiver.

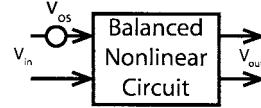

Fig. 1. Balanced nonlinear circuit stimulated with a differential input and sensed differentially at the output. The input-referred offset voltage imbalances the stimulus.

The first coefficient  $a_1$  is the small-signal voltage gain. Associated with this is an input-referred voltage intercept point for third-order two-tone intermodulation [3]

$$V_{\text{IIP3}} = \sqrt{\frac{4a_1}{3a_3}}. \quad (2)$$

Now suppose that there is a fixed offset voltage in this circuit arising from, say, threshold voltage mismatch in FETs or unbalanced bias currents in two sides of a symmetrical circuit. All internal offsets may be captured by a single equivalent offset voltage source  $v_{\text{os}}$  in series with one of the differential input terminals [2] (Fig. 1). In the presence of this offset, the differential output is

$$\begin{aligned} v_{\text{out}} &= a_1(v_{\text{in}} + v_{\text{os}}) + a_3(v_{\text{in}} + v_{\text{os}})^3 + \dots \\ &= (a_1 + 3a_3 v_{\text{os}}^2) v_{\text{in}} + \dots + 3a_3 v_{\text{os}} v_{\text{in}}^2 + \dots. \end{aligned} \quad (3)$$

The second term implies second-order intermodulation, characterized by an intercept point that depends on the offset and also on  $V_{\text{IIP3}}$  as follows:

$$V_{\text{IIP2}} = \frac{a_1 + 3a_3 v_{\text{os}}^2}{3a_3 v_{\text{os}}} = \frac{V_{\text{IIP3}}^2}{4v_{\text{os}}} + v_{\text{os}} \simeq \frac{V_{\text{IIP3}}^2}{4v_{\text{os}}}. \quad (4)$$

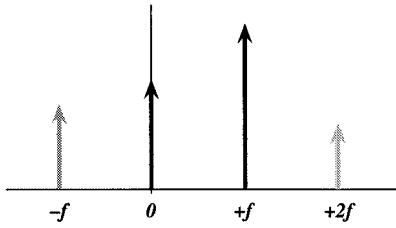

The second-order distortion arises from third-order terms because of third-order intermodulation between an input tone and the “dc tone” due to the offset (Fig. 2). To lower second-order intermodulation, i.e., to raise  $V_{\text{IIP2}}$ , offset should be lowered and  $V_{\text{IIP3}}$  should be raised. In general, offset voltage is lowered inversely with the square root of the surface area occupied by the components comprising the circuit [4]. In addition, offset at the output of a circuit that is directly coupled into a following circuit degrades the IP2 of the latter. Therefore, in the receiver's baseband or final IF section, the propagation of amplified offset from stage to stage should be suppressed by either inserting series capacitors in the signal path, or by using dc feedback around each stage.

It is well known that feedback linearizes a circuit [2], [5]. In a balanced circuit, feedback raises the third-order intercept point (IP3), and, therefore, IP2, as we will now show.

Fig. 2. Third-order intermodulation between an input tone at  $f$  and dc offset creates a component at the second harmonic. This appears like a second-order effect.

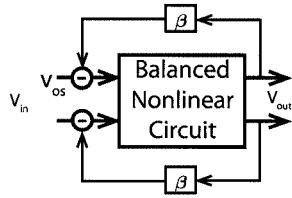

Fig. 3. Balanced nonlinear circuit with feedback applied. The feedback element is assumed linear.

#### Raising IP3 and IP2 With Negative Feedback

Suppose feedback with a factor  $\beta$  is applied around the circuit (Fig. 3). We assume that the feedback element is perfectly linear. Feedback will now try to correct the nonlinearity, and classic analysis [6],<sup>2</sup> [5], [7] shows that the input–output relation after feedback is

$$v_{\text{out}} = \frac{a_1}{1 + a_1\beta} v_{\text{in}} + \frac{a_3}{(1 + a_1\beta)^4} v_{\text{in}}^3 + \dots \quad (5)$$

The term  $a_1\beta$  is the small-signal feedback loop gain. Invoking (2), we see that feedback modifies the IP3 of the circuit as follows:

$$V_{\text{IIP3}}(\text{after } f/b) = V_{\text{IIP3}}(\text{before } f/b) \times (1 + a_1\beta)^{3/2}. \quad (6)$$

Owing to the suppression of third-order nonlinearity and for the same input-referred offset, feedback, according to (4), also raises the IP2 as follows:

$$V_{\text{IIP2}}(\text{after } f/b) = V_{\text{IIP2}}(\text{before } f/b) \times (1 + a_1\beta)^3. \quad (7)$$

This is a powerful method to raise IP2 in baseband or low-frequency parts of a receiver, where op-amp-like circuits can offer large loop gains.

Often the baseband circuits must amplify the receiver input to some prescribed full-scale output level, for instance, to the full-scale of an A/D converter. Assuming that distortion in the last stage of the baseband chain dominates, we should properly compare the output intercept point before and after feedback. Feedback still brings improvement because it follows from (6) and (7) that

$$V_{\text{OIP3}}(\text{after } f/b) = V_{\text{OIP3}}(\text{before } f/b) \times (1 + a_1\beta)^{1/2}$$

$$V_{\text{OIP2}}(\text{after } f/b) = V_{\text{OIP2}}(\text{before } f/b) \times (1 + a_1\beta)^2. \quad (8)$$

<sup>2</sup>Professor R. G. Meyer, University of California at Berkeley, pointed out this early reference.

#### Validation of General Results

These general results may be validated against Coffing and Main's analysis of the bipolar differential pair with and without degeneration. Although they have derived an expression for  $V_{\text{IIP2}}$  in the same terms as (4), it is as a preamble to the specific analysis of the circuit; they also do not bring out the relationship to  $V_{\text{IIP3}}$ .

A bipolar differential pair biased by a tail current  $2I$  obeys the following input–output relation [2]:

$$i_o = 2I \tanh\left(\frac{v_{\text{in}}}{2V_T}\right) \quad (9)$$

where  $V_T$  is the thermal voltage  $kT/q$ . The first- and third-order coefficients of a Taylor-series expansion of the right-hand side may be found in various ways. We find them by evaluating successive derivatives of the relation in (9) at the bias point, from which it follows that for an input-referred offset voltage  $v_{\text{os}}$

$$a_1 = \frac{2I}{2V_T} \quad a_3 = \frac{2I}{3(2V_T)^3} \Rightarrow V_{\text{IIP2}} = \frac{(2V_T)^2}{v_{\text{os}}}$$

and

$$V_{\text{IIP3}} = 4V_T. \quad (10)$$

As an aside, we note that  $V_{\text{IIP3}}$  of a differential pair is  $\sqrt{2}$  larger than the well-known  $V_{\text{IIP3}} = 2\sqrt{2}V_T$  of a common-emitter bipolar transistor amplifier [3], [7], which means that, in some respects, connecting two transistors into a differential pair creates a more linear circuit.

Degeneration of the differential pair by adding linear resistors  $R_E$  in series with each emitter introduces series feedback with a small-signal loop gain of  $g_m R_E$  [2], where  $g_m = I/V_T$  is the small-signal transconductance of each transistor. It then follows from the general result (7) that after degeneration

$$V_{\text{IIP2}} = \frac{(2V_T)^2}{v_{\text{os}}} \left(1 + \frac{IR_E}{V_T}\right)^3$$

and from (6) that

$$V_{\text{IIP3}} = 4V_T \left(1 + \frac{IR_E}{V_T}\right)^{3/2}. \quad (11)$$

Coffing and Main have arrived at the same expression for  $V_{\text{IIP2}}$ , but with a circuit-specific analysis.

#### REFERENCES

- [1] D. Coffing and E. Main, "Effects of offsets on bipolar integrated circuit mixer even-order distortion terms," *IEEE Trans. Microwave Theory Tech.*, vol. 49, pp. 23–30, Jan. 2001.

- [2] P. R. Gray, P. J. Hurst, S. H. Lewis, and R. G. Meyer, *Analysis and Design of Analog Integrated Circuits*, 4th ed. New York: Wiley, 2001.

- [3] B. Razavi, *RF Microelectronics*. Englewood Cliffs, NJ: Prentice-Hall, 1997.

- [4] M. J. M. Pelgrom, A. C. J. Duinmaijer, and A. P. G. Welbers, "Matching properties of MOS transistors," *IEEE J. Solid-State Circuits*, vol. 24, pp. 1433–1440, May 1989.

- [5] F. Waldhauer, *Feedback*. New York: Wiley, 1982.

- [6] A. T. Starr, *Radio and Radar Technique*. New York: Pitman, 1953, p. 416.

- [7] W. Sansen, "Distortion in elementary transistor circuits," *IEEE Trans. Circuits Syst. II*, vol. 46, pp. 315–325, Mar. 1999.

**A. A. Abidi** (S'75–M'80–SM'95–F'96) received the B.Sc. (Hon.) degree from Imperial College, London, London, U.K., in 1976, and the M.S. and Ph.D. degrees in electrical engineering from the University of California at Berkeley, in 1978 and 1981, respectively.

From 1981 to 1984, he was with Bell Laboratories, Murray Hill, NJ, where he was a Member of Technical Staff with the Advanced LSI Development Laboratory. Since 1985, he has been with the Electrical Engineering Department, University of California at Los Angeles (UCLA), where he is Professor. In 1989, he was a Visiting Faculty Researcher with Hewlett-Packard Laboratories. His research interests are in CMOS RF design, high-speed analog integrated-circuit design, data conversion, and other techniques of analog signal processing.

Dr. Abidi served as the program secretary for the International Solid-State Circuits Conference (ISSCC) from 1984 to 1990, and as general chairman of the 1992 Symposium on VLSI Circuits. He was secretary of the IEEE Solid-State Circuits Council from 1990 to 1991. From 1992 to 1995, he was Editor of the IEEE JOURNAL OF SOLID-STATE CIRCUITS. He was the recipient of the 1988 TRW Award for Innovative Teaching and the 1997 IEEE Donald G. Fink Award. He was co-recipient of the Best Paper Award presented at the 1995 European Solid-State Circuits Conference, the Jack Kilby Best Student Paper Award presented at the 1996 ISSCC, the Jack Raper Award for Outstanding Technology Directions Paper presented at the 1997 ISSCC, the Design Contest Award presented at the 1998 Design Automation Conference, an Honorable Mention presented at the 2000 Design Automation Conference, and the 2001 ISLPED Low Power Design Contest Award. He was also the recipient of an IEEE Millennium Medal. He was named one of the top ten contributors to the ISSCC.